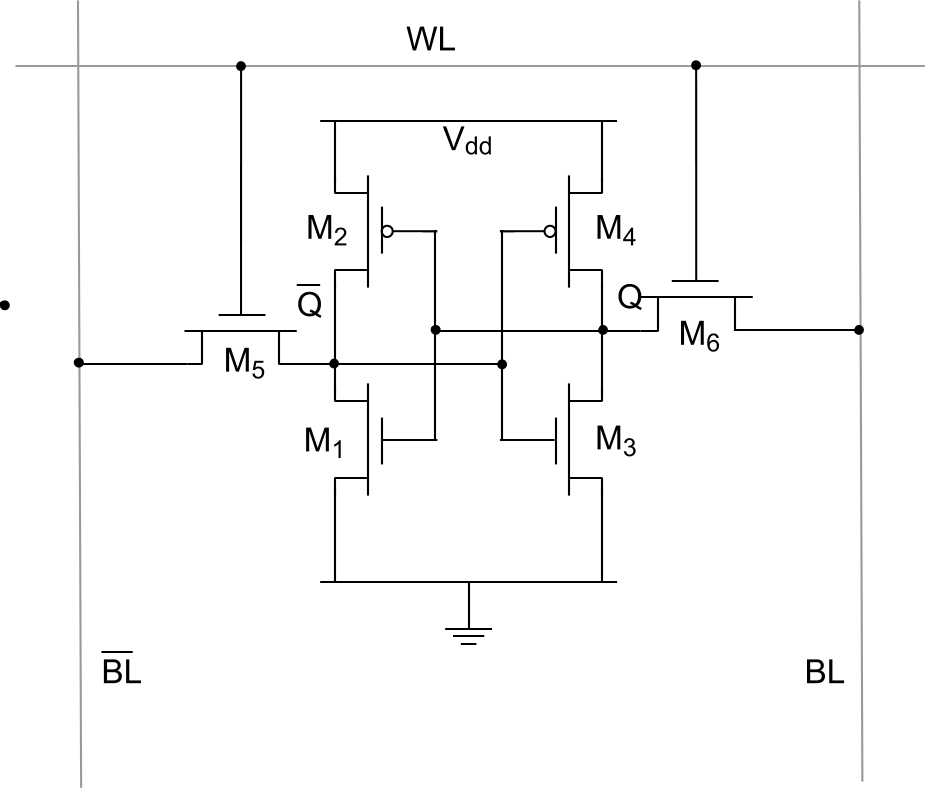

如下圖,電晶體 M1 及 M2 構成一個 inverter,M3 及 M4 構成另外一個 inverter。 這兩個 inverter 的 output 分別接到另外一個 inverter 的 input 而形成一個 latch,可以將資料鎖住。 當 Q 為 0 時,Qbar (上面一橫打不出來) 則為 1;反之 Q 為 1 時,Qbar 為 0。如此便構成了一個雙穩態電路,可以用來儲存 0 與 1。Q 和 Qbar 的寄生電容就是資料儲存的地方。 下圖剩下的兩個電晶體 M5 及 M6 功用是開關,最常見的架構和用法就如下圖所示,M5 和 M6 是一起開或關的。 連接到 M5 和 M6 的 gate 的訊號一般稱之為 word line (縮寫成 WL),是用來控制 SRAM bit-cell 開關的訊號。 當 WL 為 1 時,SRAM bit-cell 則可以讀或寫。 M5 及 M6 的 drain 端是資料讀出貨寫入的埠,一般稱之為 bit line (縮寫成 BL)。如下圖所示,M6 接到BL,相對地,M5 那邊則標成 BLbar 。 如果要將資料寫入,則要將 BL 及 BLbar 固定在一組固定的電壓,強迫 bit-cell 內儲存資料內的節點 Q 及 Qbar 轉態。如果要寫入 1 則 BL 電壓為 VDD,BLbar 電壓為 0;反之要寫入 0 則 BL 電壓為 0,BLbar 電壓為 VDD。 例如,當 bit-cell 內儲存的內容為 1 而要寫入 0。即 Q 的電壓為 VDD 時,Qbar 為 0。此時將 WL 電壓提升至 VDD 且 BL 為 0,BLbar 為 VDD,那麼 Q 就會透過 M6 被拉下來,Qbar 透過 M5 會被往上拉,再藉由 M1, M2, M3, M4 構成的兩個 inverter 推一下,則會轉態進入另一個穩態,即 Q 為 0 且 Qbar 為 VDD,寫入 0 的動作完成。 至於讀出資料時,一樣要將 word line 打開,也就是 WL 也是要拉到 VDD。和 "寫" 不同的只是 BL 和 BLbar 的狀態。將 word line 打開前要先將 BL 和 BLbar 的電壓拉到等電位,也就是 V(BL)==V(BLbar),這個電壓通常稱之為 pre-charge voltage,一般多為 VDD 或 (VDD - VT)。 當 BL 及 BLbar 兩端電位相等之後可以將之浮接 (floating) 或是透過一阻抗接至 pre-charge voltage 電壓源,然後才可以將 word line 打開,利用 Q 及 Qbar 的寄生電容透過 M6 及 M5 與 BL 及 BLbar 產生 charge sharing 及分壓的效果而讓 BL 及 BLbar 產生電位差,最後外部的 sense amplifier 可將訊號差異放大而讀出 0 或 1。 簡言之,6T-SRAM 的讀或寫都要打開 word line。寫的動作是利用外部電壓源強力改變 bit-cell 的內容。(由外影響內) 讀的動作則是將外部 BL 及 BLbar 平衡然後讓 bit-cell 的內容去影響 BL 和 BLbar。(由內影響外) 因為 bit-cell 的力量很小,BL 及 BLbar 的差異還要靠 sense amplifier 來放大。 在 VLSI 眾多領域中 SRAM 是一門獨立大學問,只是一個 6T-SRAM bit-cell 就有讀不完的論文,這實在不是知識+ 一個問題的問與答就可以說清楚的。 1. YES, bit-cell 儲存值就是指 Q 的值。 2. YES, BL 下降而 BLbar 不下降為 0,反之 BLbar 下降而 BL 不降則為 1。Sense amplifier 是用來放大 BL 跟 BLbar 的差異,然後才可以啟動後級的電路將訊號輸出。

留言列表

留言列表

{{ article.title }}

{{ article.title }}